SoC Blockset

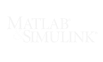

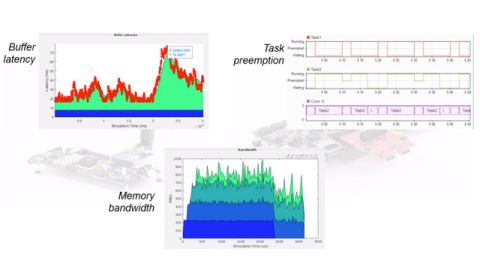

SoC Blockset enables you to simulate and analyze the performance of algorithms on programmable SoCs and ASICs. You can deploy these algorithms as hardware and software applications for prototyping and production.

The blockset lets you build Simulink models of hardware architectures by defining interfaces between Arm® processor cores, hardware logic, memory, and peripherals. You can use models to partition algorithms between hardware logic and processors to analyze implementation tradeoffs.

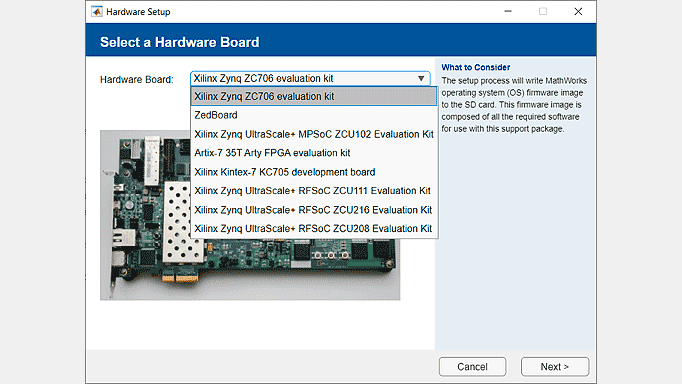

The SoC Builder app automates deployment by building IP cores and software, then programming development boards (with HDL Coder and Embedded Coder).

SoC Blockset analyzes applications in hardware with performance diagnostics and software profiling. Supported devices include AMD® Versal™ Adaptive SoCs, Zynq™ UltraScale+™ MPSoCs/RFSoCs, and Zynq-7000 SoCs, as well as Intel® SoC FPGAs.

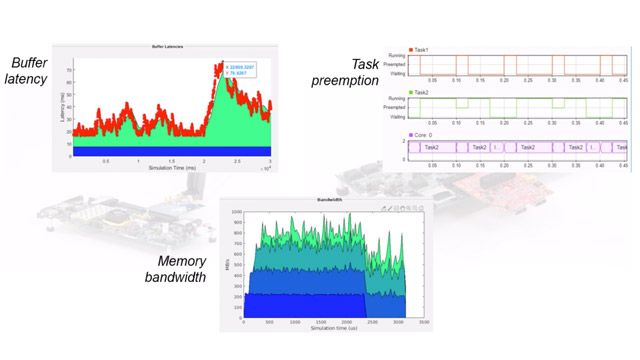

5G and SDR Applications

Simulate and deploy 5G NR MIB or SIB1 recovery algorithms for FR1 and FR2 using Wireless HDL Toolbox and SoC Blockset. Prototype, verify, and test wireless systems with Zynq-based radios and Analog Devices RF cards.

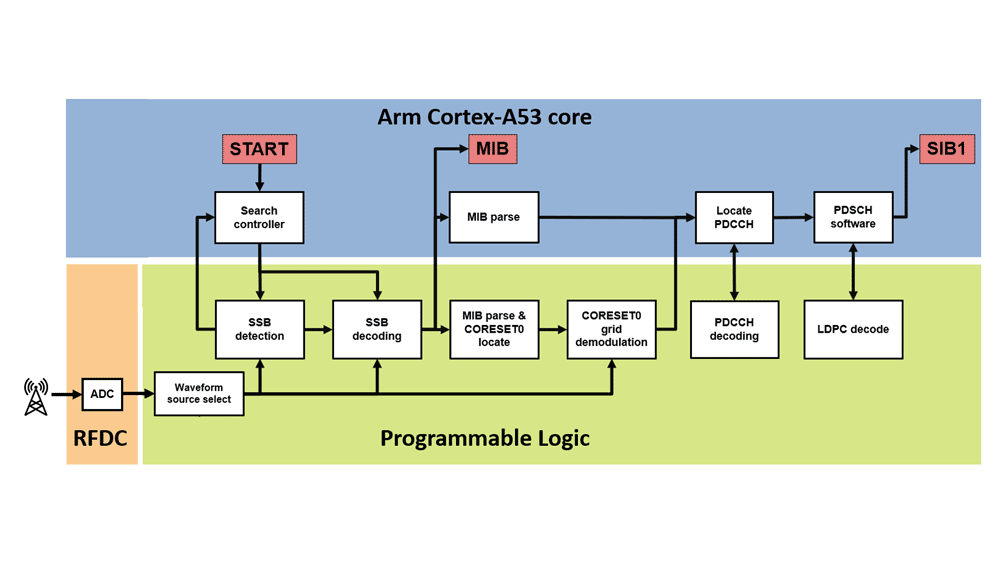

Vision Applications

Build models with SoC reference designs to capture live video, process video streams on hardware, and integrate with deep learning processors. Develop prototype designs using the SoC Blockset hardware support package for live video input.

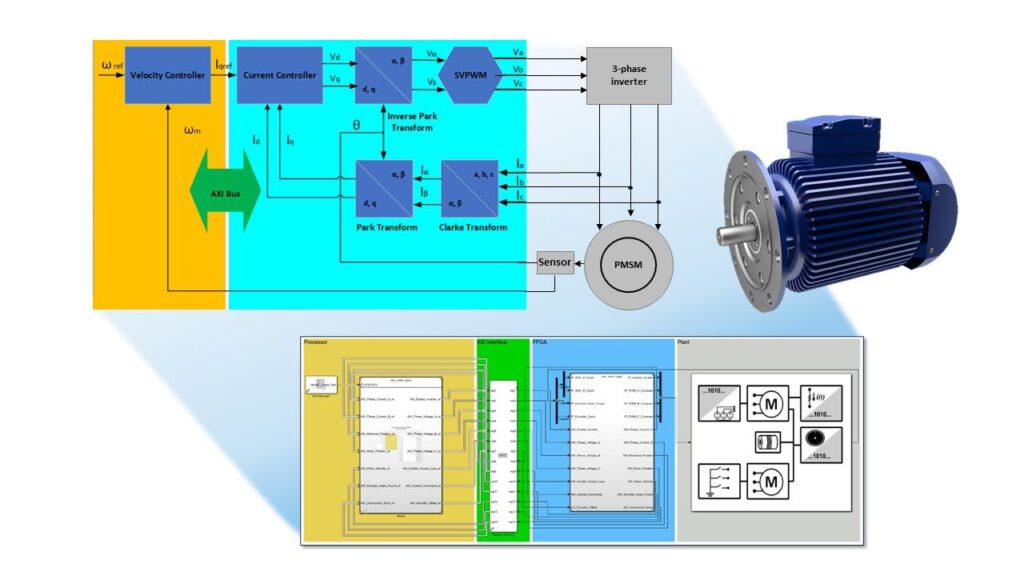

Motor and Power Electronics Controls Applications

Model and simulate motor and power electronics controllers partitioned between processors and programmable logic. Automate C code and IP core generation for targeting AMD Zynq, Versal devices, and Intel SoC FPGAs.

Target Versal Devices

Analyze system designs with predefined models of the latest AMD programmable SoC devices, then deploy them to development boards for testing using the SoC Builder tool.

Target RFSoC Devices

Simulate and deploy radar applications to AMD RFSoC devices, targeting 5G signal detection. Use SoC Blockset to program hardware, load test data, and control the design. Implement frequency-hopping algorithms for CDMA and FHSS on AMD UltraScale+ RFSoCs.

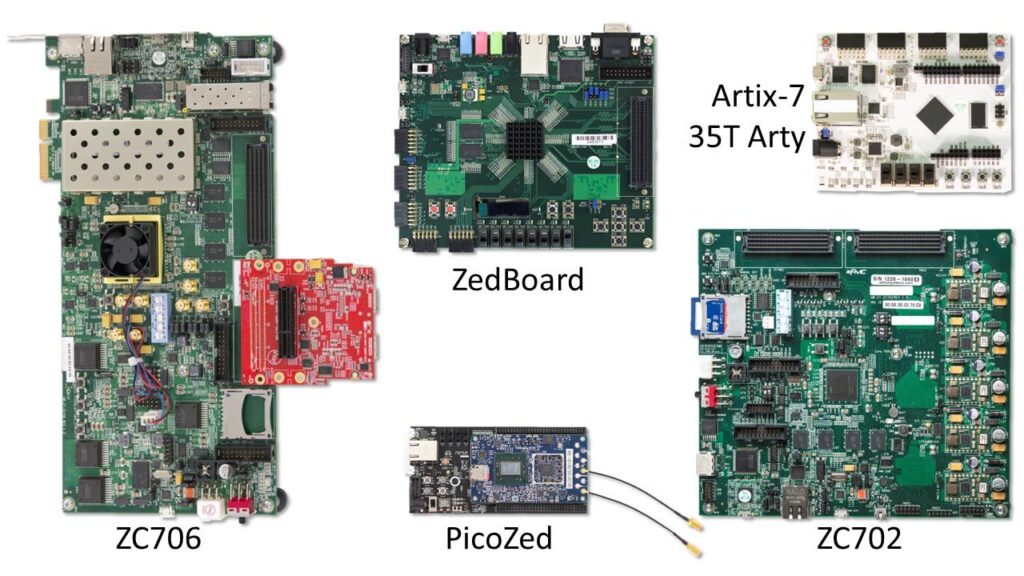

Target AMD UltraScale+ MPSoC and Zynq-7000 Devices

Develop motor/power electronics controls or wireless communications for MPSoC and Zynq-7000 platforms. Use the SoC Builder app to configure, build, and deploy hardware/software algorithms for hardware prototyping.

COTS Boards and Custom Board Support

Use the OS Customizer tool to modify and add libraries to the Linux® distribution for your embedded processor, customizing the embedded Linux OS on supported boards.

Model DDR Memory

Model DDR memory and simulate shared memory access between logic and processors. Configure DMA controllers and include memory latency and throughput in simulations.

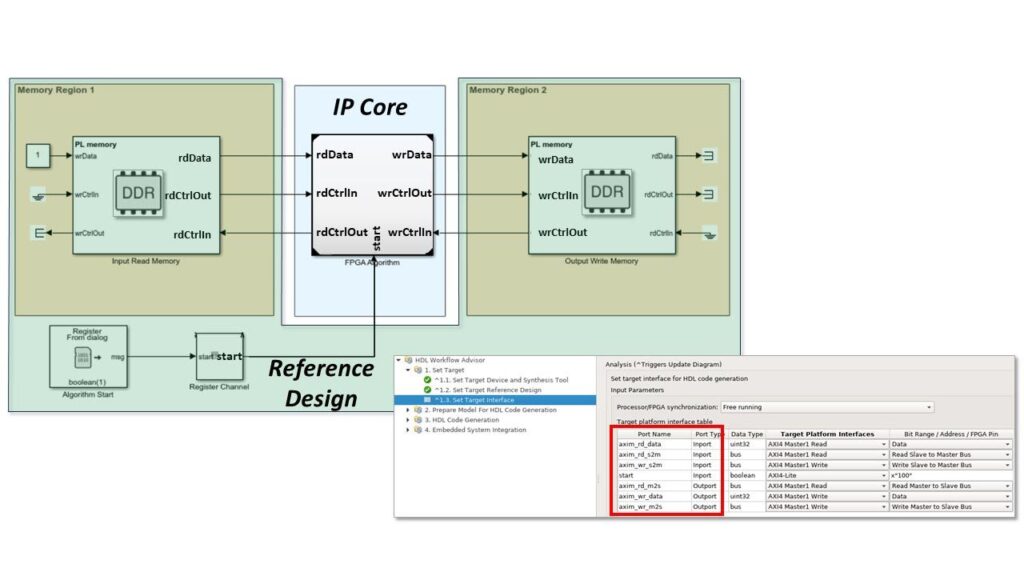

Generate HDL Coder Reference Designs

Generate HDL reference designs from SoC Blockset models and integrate HDL Coder IP cores using the HDL Workflow Advisor.