Stateflow

Stateflow provides a graphical language for designing state transition diagrams, flow charts, and tables to describe how MATLAB algorithms and Simulink models respond to inputs, events, and time conditions. It’s used for applications like supervisory control, task scheduling, fault management, communication protocols, and hybrid systems.

You can model both combinatorial and sequential decision logic, simulate within Simulink, or execute as a MATLAB object. Stateflow offers graphical animations to analyze and debug logic during execution, with edit-time and run-time checks to ensure design consistency and completeness before implementation.

Design State Machines

Design state machines in Stateflow using drag-and-drop elements and simple logic statements. Stateflow Onramp and training resources are available to help you get started quickly.

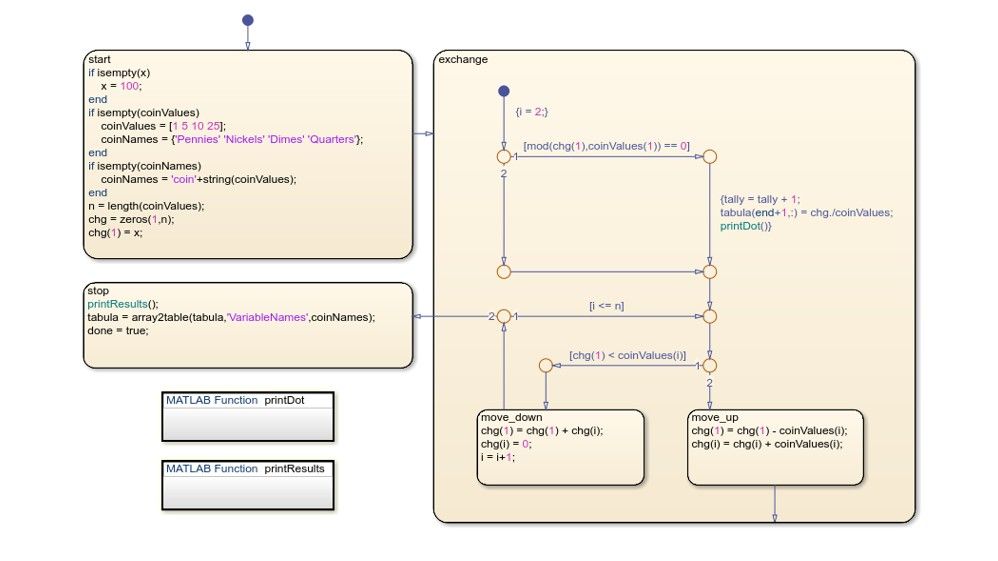

Create Flow Charts

Use flow charts to represent state logic, and leverage the Pattern Wizard to automatically generate flow charts for common logic patterns.

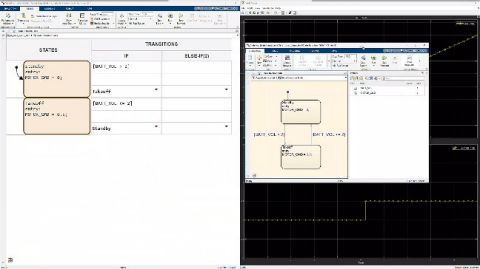

Model Logic with Tables

Stateflow includes State Transition Tables for modeling logic in a tabular format and Truth Tables for implementing combinatorial logic design.

Execute Stateflow Charts

State diagram execution includes animations that highlight active states and transitions. You can also modify variables during execution to visualize their impact on the system.

Monitor and Analyze Data

Simulation Data Inspector lets you visualize simulation data, enabling you to monitor system behavior and gain valuable insights.

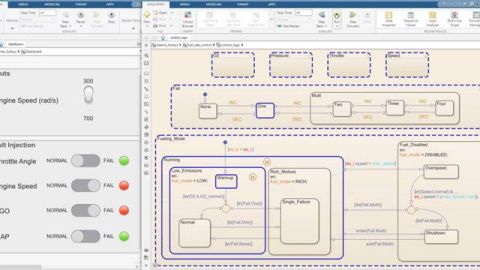

Debug Logic in Stateflow

Stateflow offers debugging tools to step through chart execution, set breakpoints, and analyze functions in state diagrams to identify and resolve unexpected behavior.

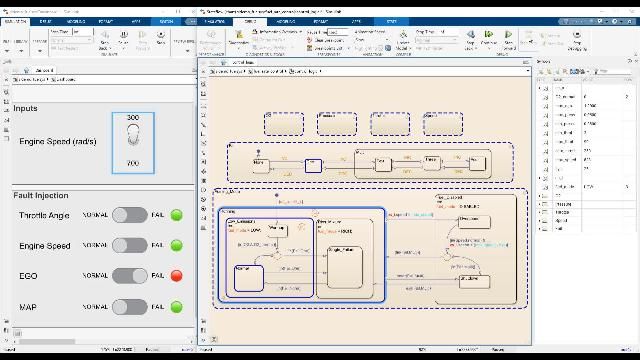

Stateflow Task Scheduling

Stateflow can invoke Simulink algorithms periodically or continuously, scheduling component execution and simulating real-time environments.

Validate Designs with Simulink

Stateflow integrates with other MathWorks products to verify, validate, and test designs, ensuring they meet requirements, detect errors early, and achieve quality objectives.

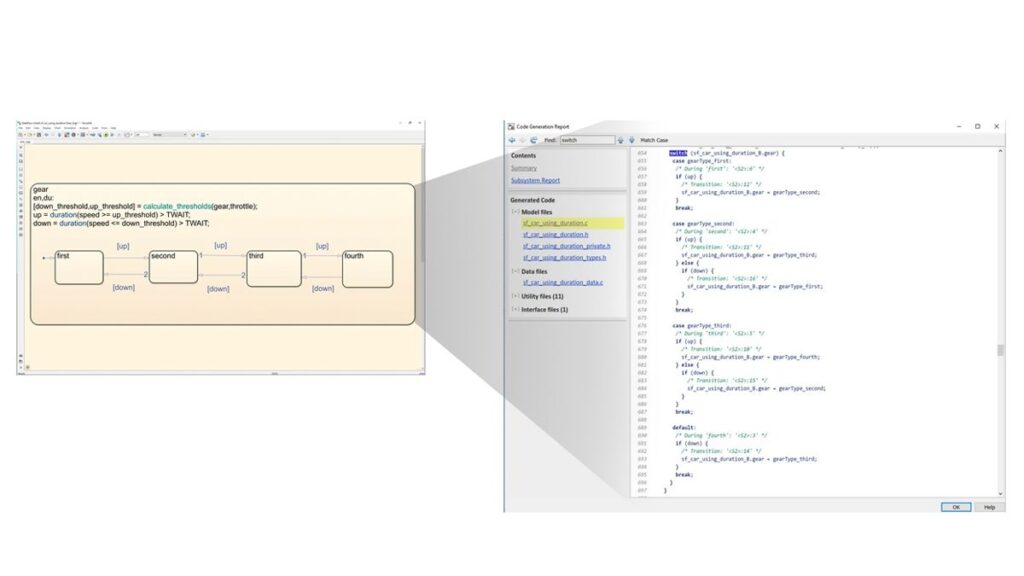

Generate Code for Deployment

Stateflow enables code generation for state chart logic on embedded systems, supporting C, C++, VHDL, Verilog, and Structured Text for PLCs.