Wireless HDL Toolbox

Wireless HDL Toolbox provides pre-verified Simulink blocks and subsystems for developing 5G, LTE, WLAN, satellite (DVB-S2, GPS, CCSDS), and custom OFDM-based wireless communication applications. It includes reference applications and IP blocks that can be modified for custom designs.

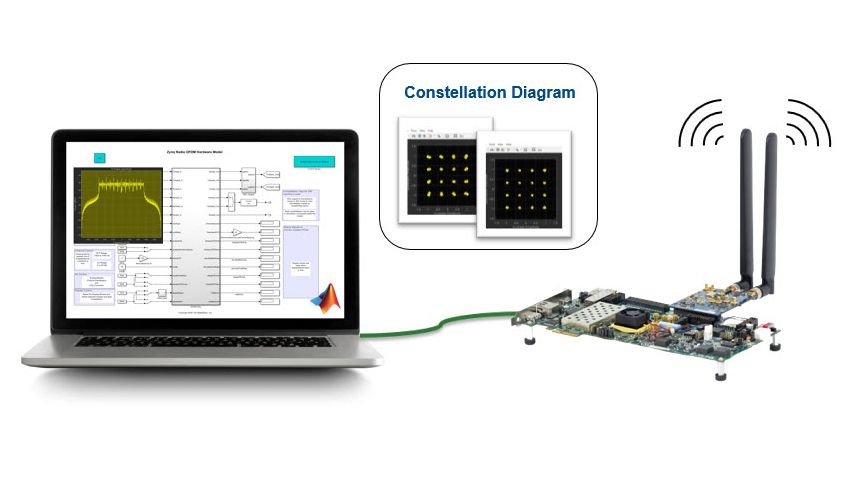

The toolbox generates optimized, synthesizable VHDL® and Verilog® code, suitable for FPGA, ASIC, and SoC devices. You can verify the code on FPGA hardware via FPGA-in-the-loop cosimulation and generate SystemVerilog DPI components for verification with HDL Verifier. For over-the-air testing, transmitter and receiver models can be connected to radio devices using Communications Toolbox and SoC Blockset support packages.

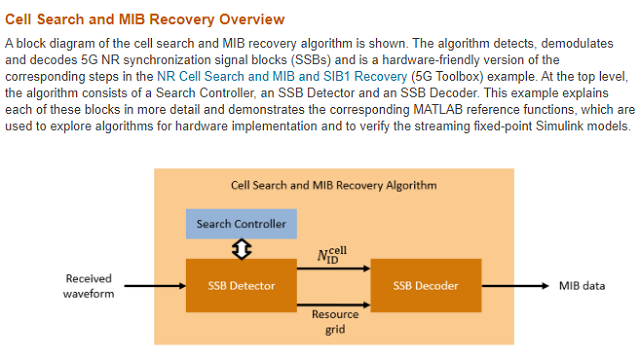

5G New Radio (NR)

Integrate prebuilt and verified 5G NR subsystem IP for cell search and MIB/SIB1 recovery. Design custom 5G subsystems for hardware using 5G NR IP blocks, including LDPC, Polar, and CRC.

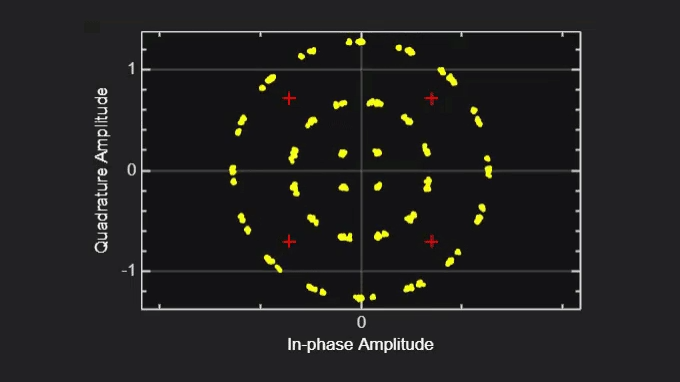

Configurable OFDM

Transmit and receive data using OFDM hardware subsystem IP. Design custom OFDM-based FPGA or ASIC hardware with HDL-optimized IP blocks.

Satellite Communications

Design satellite communication systems based on DVB-S2, CCSDS, and GPS for FPGA or ASIC implementation. Integrate subsystem IP like a DVB-S2 receiver, or create custom systems using HDL-optimized IP blocks.

WLAN

Develop wireless LAN communication systems for FPGA or ASIC hardware. Start with a WLAN receiver or time and frequency synchronization subsystem, or create custom functionality using IP blocks.

LTE

Integrate prebuilt and verified 4G LTE subsystem hardware IP for tasks like cell search, MIB/SIB1 recovery, or a MIMO LTE transmitter.

Custom Communications

Use hardware-proven building block IP to develop custom communications systems. Get started quickly with example designs such as a digital pre-distorter (DPD) or generic low-density parity-check (LDPC) encoder and decoder.

Verification

Simulate hardware-ready models and compare results with MATLAB reference algorithms. Use HDL Verifier for cosimulation with generated HDL or to create models for RTL verification.

FPGA, ASIC, and SoC Deployment

Use HDL Coder to deploy your application on FPGA-based software-defined radio (SDR) platforms, enabling prototyping with live over-the-air signals. The same application models can be reused for production deployment.